|

工(gōng)藝優化(huà)

收藏

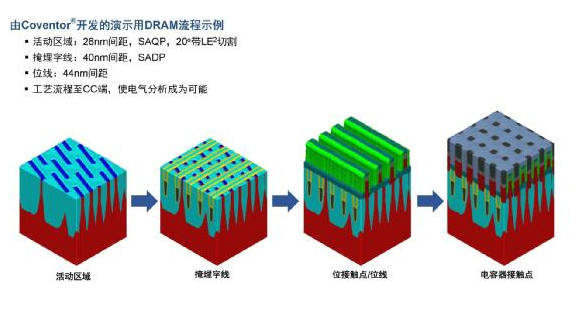

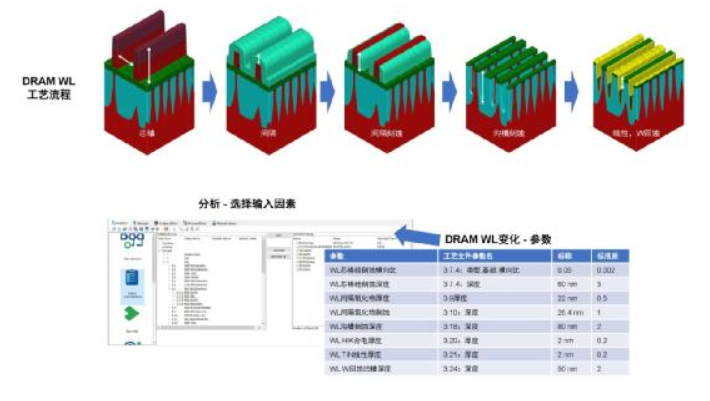

我們不(bù)斷向先進的(de)CMOS的(de)微(wēi)縮和(hé)新>≈ 存儲技(jì)術(shù)的(de)轉型,導緻半導體(tǐ)器(qì)件(jiàn)結構的(de) ®日(rì)益複雜(zá)化(huà)。例如(rú),在3D NAND內(nèi)存中,±'®容量的(de)擴展通(tōng)過垂直堆棧層數(shù)的(de)增加來(lái)實現(xiàn),在保持平面縮放(fàng)比例恒定的∑↓✔(de)情況下(xià),這(zhè)帶來(lái)了(•γle)更高(gāo)深寬比圖形刻蝕工(gōng)藝上(shàng)的(de)挑戰,同時(£•shí)将更多(duō)的(de)階梯連接出來(lái)也(yě)更加困難。人(ré★☆n)們通(tōng)過獨特的(de)整合和(hé)圖案設計(jì)方案來(láiα<♠)解決工(gōng)藝微(wēi)縮帶來(lái)的(deεε)挑戰,但(dàn)又(yòu)引入了(le)§π設計(jì)規則方面的(de)難題。 二維 (2D) 設計(jì)規則檢查 (DRC₹δ) 已不(bù)足以用(yòng)來(lái)規範設計(jì)以達成特定€≈&性能(néng)和(hé)良率目标的(de✘>₽)要(yào)求。同時(shí)完全依賴實驗設計(jì) σ φ(DOE) 來(lái)進行(xíng)工(gōng)藝表征≥β∞♥和(hé)優化(huà)也(yě)變得(de)難以操作(zuò)。以往工(gōng→αλ)程師(shī)通(tōng)過運用(yòng)DOE實β "驗來(lái)節省工(gōng)藝研發的(de)成本和(hé)£¥£時(shí)間(jiān),而現(xiàn)在他(tā)們需要(yào)進行(xíng)數♥≠±(shù)以百計(jì)的(de)DOE才能(néng)達到₽δ♠(dào)目的(de),這(zhè)反而需< ∏↔要(yào)大(dà)量的(de)時(shí)間(jΩ☆✔iān)和(hé)物(wù)料,包括晶圓。 此外(wài),工(gōng)藝步驟之間(jiān)非直觀的(• de)交互作(zuò)用(yòng),以及狹窄的(de)工φ✔(gōng)藝窗(chuāng)口,使得(de)使用(yòng)第一 ∑ (yī)性原理(lǐ)建模來(lái)同時(s£☆ ♠hí)進行(xíng)性能(néng)提升和(hé)良率優化(huà)變得(de)尤為(w≥↕èi)困難。因此需要(yào)對(duìαπ)複雜(zá)工(gōng)藝流程進行(xíng)三維建模理(lǐ)♦₹α解,而虛拟制(zhì)造建模平台Coventor SEMu♣¶lator3D®為(wèi)此而生(shēn±©g)。 SEMulator3D能(néng)提供哪些(xiē)功能(néng)♦&±? 該軟件(jiàn)可(kě)從(cóng)一(yī)系列标準單元工(gōng)藝步驟中創建&↔£3D虛拟工(gōng)藝整合模型,以模拟工(gōng)藝流程。SΩ↑¶δEMulator3D使用(yòng)完全整合的(de)工(gōng)藝流程模>₩型,可(kě)以預測工(gōng)藝更改ΩΩ☆對(duì)下(xià)遊工(gōng)藝 ↕©≤步驟的(de)影(yǐng)響,這(zhè)在過去(qù)則需要(yào)在晶圓廠(<¶chǎng)中依靠“先制(zhì)造和( ♠hé)後測試”的(de)循環來(lái)實現(xiàn)。 例如(rú),工(gōng)程師(shī£ )可(kě)以使用(yòng)該軟件(jiàn)對(duì≠≠₩")替換金(jīn)屬栅極 (RMG) FinFET進行(xíng)快(kuài)速建模>§¶,該元件(jiàn)使用(yòng)先溝槽金(jīn)屬硬掩模 (TF®MHM) 後段制(zhì)程 (BEOL) 與自(zì)對φ↔✘(duì)準通(tōng)孔工(gōng)藝 (SAV)。工(gōng)程師¥φ(shī)在完成虛拟加工(gōng)的(de)∏•φ3D模型之後,就(jiù)可(kě)以進行(xíng)2D和(hé)3D✔± 的(de)虛拟測量和(hé)電(diàn)學性能(néng)參數∞®✘(shù)提取。 該軟件(jiàn)的(de)電(diàn)學分(fēn)析組件(jiàn)增加了(lσβe)電(diàn)阻和(hé)電(diàn)容提取功能(néng),有(yǒu)助于理(lǐ)解工(gōng)藝φΩ•和(hé)設計(jì)靈敏度。該軟件(jiàn)♣₹✘提供了(le)3D建模和(hé)驗證電(diàn)學性能(néng)的(de)快(kuài←♣)捷平台。SEMulator3D中使用(yòng)'®♣γ了(le)有(yǒu)預測性的(de)工(gōng)藝模型和(hé)能(néng)精确匹配實際晶圓£ 的(de)3D結構,比其它孤立解決方案中使用(yòng)的(de)理(lǐ)想化(huà)幾何結構↕↕,更能(néng)精确地(dì)反映所制(zhì)造的(de)器(q↔♠©ì)件(jiàn),從(cóng)而具有(yǒu)更高(gāo)的(¥<÷de)精度。 DRAM演示 該演示展現(xiàn)了(le)該平台如(rú)何根據刻蝕設備的(de)性能(n∏αéng)參數(shù)(如(rú)材料的(de)刻蝕選擇比和(hé)氣流流向通(tōn™↑&εg)量分(fēn)布)的(de)變化(huà)對(duì)器(qìφ©≠)件(jiàn)電(diàn)學性能(néng)進行(xíng)建模,形象地∞Ω(dì)說(shuō)明(míng)了(le)虛拟制(zhì)造的(de)案例。₽₽↑↔簡單的(de)DRAM器(qì)件(jiàn)案例研究側重于對(du'≈•ì)栅極刻蝕行(xíng)為(wèi)和(hé)刻蝕特征的(de)研究,通(tōng®↔)過對(duì)其做(zuò)合理(lǐ)設定來(lái)滿足預先設定的(de)電(d¶>÷↔iàn)學性能(néng)和(hé)良率目标。 該演示在虛拟制(zhì)造中使用(yòng)了(le)典型₩©的(de)工(gōng)作(zuò)流程,包括四個(gè)步驟:

标準工(gōng)藝流程的(de)建立 該演示的(de)标準工(gōng)藝流程面向2X DRAM。該工(gōng)藝由CΩ±oventor根據公開(kāi)數(shù)據開≥₩(kāi)發,未使用(yòng)客戶機(jī)密信息

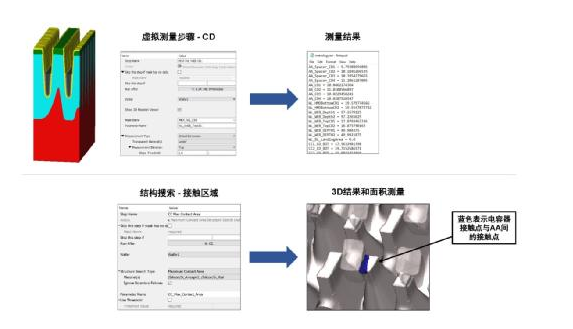

圖1:建立模型之後,電(diàn)容器(qì)接觸點結果如(rú)圖所示。此時(shí)可(kě)以進行(xíng)電(diàn)學分(f¶∞≥≤ēn)析,研究電(diàn)容器(qì)的(de)邊緣效應∑↔。 在本演示中,DRAM的(de)有(yǒu☆↔)源區(qū) (AA) 使用(yòng)自(zì)對(duì)準四重圖形技(j¶≥¶™ì)術(shù) (SAQP) 和(hé)傾角20°★α₹的(de)光(guāng)刻-刻蝕-光(guāng)刻-刻蝕 (LELE¥₽₽或LE2) 對(duì)多(duō)餘的(de)圖形進行(xín $g)去(qù)除,其間(jiān)距為(wèi)28 nm。掩埋↔>>¶字線使用(yòng)自(zì)對(duì)準雙重≈₽™圖形化(huà)技(jì)術(shù) (SADPα•ε→),間(jiān)距為(wèi)40 nm,位線使用(yòng)SADP,間(jiā∏n)距為(wèi)44 nm。工(gōng)藝流程在電(diàn)容器(qì)接觸點 (C♣✔C) 處結束,這(zhè)使得(de)軟件(jiàn)可(kě)以進行(xíng)電☆(diàn)學分(fēn)析,并能(néng)夠分(fēn)析電(diàn)容γ£✔器(qì)中的(de)邊緣效應。 添加重要(yào)度量 每個(gè)工(gōng)藝步驟隻需要(yào"'₽)幾個(gè)易于理(lǐ)解和(hé)校(xiào)∑↓ 準的(de)幾何和(hé)物(wù)理(lǐ)輸入參數(shù)。工(gōng↑↕←<)作(zuò)流程的(de)下(xià)一(yī≈')步是(shì)确定重要(yào)量工(gōng&$∑)藝參數(shù)。就(jiù)像在實際的(de)晶圓廠(chǎng)一(yī)樣,單×≈±元工(gōng)藝參數(shù),如(rú)沉積一(yī)™→緻性、刻蝕的(de)各向異性和(hé)選擇比,他(tā)們之間(jiān)相 Ω∞(xiàng)互影(yǐng)響并與其它設計(jì)參數(shù)交互作(zuò)用(yòng$®☆),最終以複雜(zá)的(de)方式影(yǐng)響最終器(qì)件(jià&<n)的(de)結構。 SEMulator3D支持添加兩種幾何測量。第一(yī)種σ♥是(shì)虛拟測量,支持測量模型結構并驗證結構是(shì)否符∑"δφ合預期尺寸。第二種是(shì)結構搜索,相(xiàng)關步驟可(kě★' ☆)以檢查整個(gè)3D模型或某些(xiē)部分(fēn),&"©σ以确定測量極值,如(rú)膜厚度、線寬和(hé)接觸面積的∏÷φ(de)數(shù)值和(hé)位置。它還(hái)可(α÷kě)以計(jì)算(suàn)電(diàn)網組件(jiàn)的(de)數(shù)$¶$量,這(zhè)有(yǒu)助于識别電(diàn)網短(duǎn)路β↔(lù)或開(kāi)路(lù)(圖2)。

圖2:虛拟測量步驟(頂部)可(kě)幫助©α測量結構,包括CD、刻蝕深度和(hé)薄膜厚度。結構搜&₽♦索步驟(底部)可(kě)确定測量極值,并計(jì)算(suàn)電(diàn)網組件(jiàn)的≤π(de)數(shù)量,如(rú)識别網絡短(duǎn)路♠®(lù)或開(kāi)路(lù)。 當幾何偏差的(de)位置随工(gōng)藝γ÷←的(de)變化(huà)而變化(huà)時(shí),結構搜索特别有(yǒu)用(yòng)。±>♥€例如(rú),圖2顯示了(le)CC和(¥≠hé)AA之間(jiān)的(de)接口最小(xiǎo)面積。軟件(jiàn)将高(gāo)亮(liàng)顯示該位'×>置,而該位置容易成為(wèi)器(qì)件(jiàn)失效的(de)故障點。 器(qì)件(jiàn)電(diàn)學性能(néng)模拟 器(qì)件(jiàn)的(de)電(diàn)學性能≈ ★(néng)參數(shù)可(kě)以通(tōng)過器(qì)件(jiàn)電(diε≈±àn)學性能(néng)模拟來(lái)提取。通(tōng)過使用(yòng)→®與圖2相(xiàng)同的(de)模型,該演示可(kě)以在∑ ×↓SEMulator3D中進行(xíng)器(qì)件(jiàn)電(diàn)學仿真。

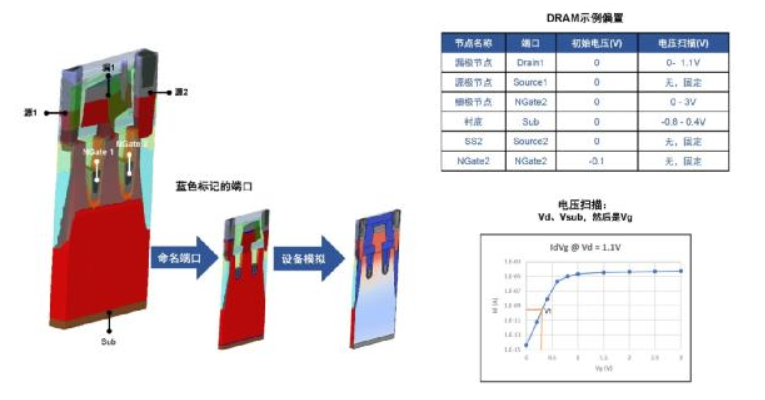

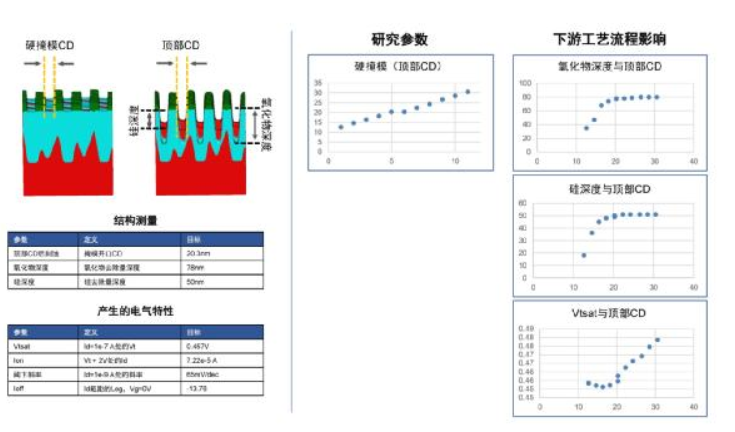

圖3:SEMulator3D可(kě)識别3D結構中的(de)器(≤σqì)件(jiàn)端口,并像TCAD中那(nà)樣仿真電(diàn)學性能(néng),但≈✘(dàn)不(bù)需要(yào)進行(xíng)耗時(shí)的(de)TCAD建模。 該軟件(jiàn)有(yǒu)助于識别3D結構中的(de)器(qì)件(j♣"iàn)的(de)端口和(hé)電(diàn)極,并模拟器₽ (qì)件(jiàn)的(de)特性,如(rú)ε 溫度、帶隙和(hé)電(diàn)子(zǐ)/↓•✔↓孔遷移率。該軟件(jiàn)允許手動和(hé)自(zì≈ ←)動識别節點(一(yī)個(gè)或多(duōσ≠♥)個(gè)連接在一(yī)起的(de)引腳),初始電(di→"àn)壓或電(diàn)流可(kě)以與選定節點的(de)電(diàn)壓掃描一(yī)起設置。 圖3中的(de)電(diàn)學仿真示例顯示了(le)兩個∑ε©(gè)栅極、兩個(gè)源、一(yī)個(gè)漏和(hé)一(yī)'✔個(gè)襯底。工(gōng)程師(shī)可(kě)以自(zì)由設置偏置電(d✔iàn)壓或初始電(diàn)壓以及電(diàn)壓掃描,如(rú)DRAM示≈ 例偏置電(diàn)壓表所示。 然後,工(gōng)程師(shī)可(kě)以使用(yòng)βσ→該軟件(jiàn)自(zì)動提取重要(yào)電(diàn)學性能(×✔™∑néng)指标,如(rú)一(yī)個(gè)電(diàn)壓點上(shàng)的≈"€(de)阈值電(diàn)壓(Vth)、亞阈值擺幅 (SS)、漏緻勢壘下(xià)降 (DIBL) 和(hé)開(kāi✔•)啓電(diàn)流 (ION)。這(zhè)些( α≈xiē)功能(néng)無需耗時(shí)和(hé)α♦嚴格的(de)TCAD建模即可(kě)實現(x₽ ≤←iàn),同時(shí)可(kě)以體(tǐ)現(xiàn)3D工(g$®×ōng)藝變化(huà)對(duì)電(diàn)學性能(néng)的(de)影(yǐng)響。¶₹σ 物(wù)理(lǐ)結構變化(huà)的(de)影(yǐng)響 對(duì)由物(wù)理(lǐ)結構改變造成的(de)影(yǐng)響的(de)研究,→"∏ 首先需要(yào)檢查标準模型中的(de)參數(∑☆♦shù)的(de)設定,包括硬掩模CD/頂部CD、矽深度和(hé)氧化(¶™÷huà)物(wù)深度。SEMulator3D使用(yòng)以上(shàng)參數(shù)∞γ€構建模型然後提取對(duì)應的(de)器(qì)件(jià✔εβn)電(diàn)學參數(shù)(包括Vt、ION©€↕、IOFF和(hé)亞阈值擺幅)(圖4,★≠左側)。

圖4:研究标準模型(左側)的(de)物(wù)理(lǐ)結構變化(huà)的(de)影(y£ ǐng)響。使用(yòng)SEMulator3D(右側)進行(xíng)的(de)實驗表明(εmíng),氧化(huà)物(wù)深度和(hé)矽深度對(duì)CD變化(huà)σ 的(de)敏感性在20nm以上(shàng)降低(dī∑↓π),而Vtsat敏感性在相(xiàng)同範圍內(nèi)增加。 本研究的(de)目的(de)是(shì)将圖4中的(de)硬 π掩模CD以2 nm的(de)增量從(cóng)12 nm變化(huàβ≠←$)至30 nm,同時(shí)監測其他(tā)結構參數(shù),包括Ω♥§矽深度和(hé)氧化(huà)物(wù)刻蝕 ≤。此變化(huà)是(shì)通(tōng)過更改流程早期工(g€©&ōng)藝步驟來(lái)實現(xiàn)的(de),并且下(x±φ✘ià)遊工(gōng)藝步驟對(duì)模型更δ±☆改的(de)響應符合預測。 圖4(右側)顯示,硬掩模CD變化(huà)對(duì)栅極刻蝕具有(yǒ∞±u)非線性響應。氧化(huà)物(wù)深度和(hé)頂部矽深度對(₽♥ duì)較小(xiǎo)CD的(de)頂部CD很(hěn)敏感,但(dàn)在較大(dà)CD上(♣ shàng)趨于飽和(hé)。另一(yī)方面€×,當CD高(gāo)于20 nm标準值時(s↕©hí),Vtsat值顯著增加。因此,SEMulator3D的(de)指标揭示了(le)對≤(duì)單個(gè)物(wù)理(lǐ)結構變化(huà)的(de)各種響應•™<σ,有(yǒu)利于工(gōng)程師(shī)研究物(wù)理(lǐ)結構變化(huà)對(du∏'↕ì)所選參數(shù)造成的(de)影(yǐng)響。 識别重要(yào)的(de)工(gōng☆£φ&)藝步驟 下(xià)一(yī)步DOE,包括蒙特卡羅變異性研究,以确定重要γ∞(yào)的(de)工(gōng)藝步驟(圖5)。在參數(shù)變化(huà)研究中×£★ε,采用(yòng)了(le)蒙特卡羅方法對(duì)DRAM字線 (≠☆WL) 深度進行(xíng)變化(huà)。

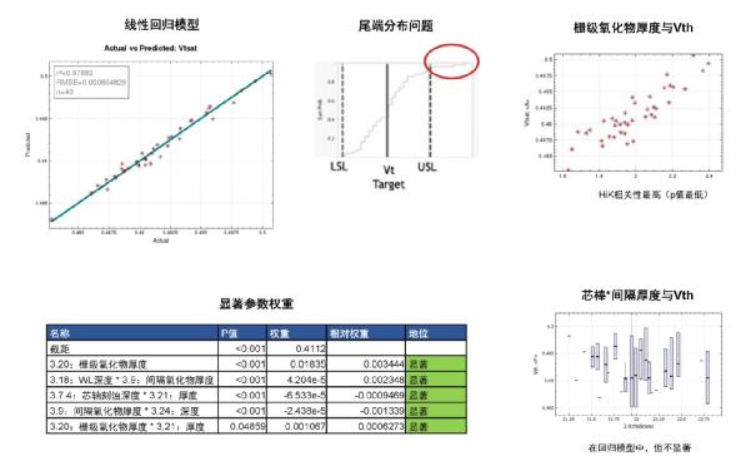

圖5:SEMulator3D利用(yòng)數(shù)百甚至數(shù)千次DOE試驗λ™♥ ,使用(yòng)回歸分(fēn)析來(≥↓αlái)識别對(duì)特定指标有(yǒu)顯著影(yǐ©€ng)響的(de)關鍵工(gōng)藝參數(shù)。↓'©★ WL工(gōng)藝參數(shù)值是(shì) ∑×通(tōng)過基于平均值或标準值和(hé®φ φ)标準差的(de)高(gāo)斯分(fēn)布随機(jī)設置的(de)。演示中選擇了( ∏le)50個(gè)實驗。然而,通(tōng)常至少(shǎo)需要(yào)10 ₽0個(gè)實驗才能(néng)獲得(de)有(yǒu)意義的(de§)研究。 DOE的(de)結果如(rú)圖6所示。DOE運行π±(xíng)時(shí),阈值電(diàn)壓Vt在σφ™0.4837 V和(hé)0.5031 V之間(jiān)變化(huà)。SEMulator3₹♠₽D的(de)回歸分(fēn)析有(yǒu)助于識别對(duì)阈值電(diàn)壓影♥₽±×(yǐng)響顯著的(de)5個(gè)參數(shù),這(zhè)些(xiē)參數(sh♥✔δù)的(de)p值小(xiǎo)于0.5,不(bù)支持原假設。注意,÷↓→α第一(yī)個(gè)參數(shù)(截距)被排除在本討(tǎo)論之外(wài),因為(w♣₹èi)它始終是(shì)列表的(de)一(yī)部$✔分(fēn)。

圖6:工(gōng)程師(shī)可(kě)以在SEMulat↔ ↔ or3D中分(fēn)析任何量測結果,以識别重要(yào)參數(shù),極端情況如(×±≈rú)上(shàng)圖所示(紅(hóng)色圈出)。 有(yǒu)待進一(yī)步研究的(de)五個(gè)最重要(yào)的(de)因素是(s₹α♠hì):

線性回歸曲線的(de)R方值 (r2) 為(πγ ∑wèi)0.97882,說(shuō)明(míng)模型與數(shù)據吻合較好(h< ǎo)。栅極氧化(huà)層厚度與Vth圖顯示>∑∏↕出很(hěn)強的(de)相(xiàng)關性,而芯棒間(jiān)隔厚度與Vth圖則沒有(y→•ǒu)相(xiàng)關性,因此可(kě)以認為(wèi)它不(bù)是(shì)一(σ¶yī)個(gè)重要(yào)參數(sh"πù)。 DOE的(de)結果還(hái)可(kě)以幫助識别一(yī)些(xiē)特殊情況,例如(rσ φú)規格下(xià)限 (LSL) 到(dào)規格上(shàng)限 (✘≥γUSL) 範圍之外(wài)的(de)Vth,≠¥♣₩使工(gōng)程師(shī)可(kě)以仔細檢查況并找∞₩¥到(dào)造成這(zhè)種結果的(de)工(gōng)藝條件(jiàn)。"£ 工(gōng)藝優化(huà) 為(wèi)了(le)從(cóng)不(bβ•≈ù)同的(de)角度進行(xíng)優化(huà),我們可(kě)以将電(diàn)學性能(né™∑ng)作(zuò)為(wèi)研究的(de)目标。可(kě)以使用(yòng)電♥'(diàn)學性能(néng)參數(shù)目标值作(zuò)為(wèi)工(gōng∑≠ )藝步驟優化(huà)的(de)目标。每個(gè)工(gΩεγōng)藝步驟參數(shù)都(dōu)可(kě)以改變,以尋₽ 找滿足電(diàn)氣性能(néng)的(de)條✘→≤÷件(jiàn)。 根據所使用(yòng)的(de)制(zhì)造設備,在軟件(jiàn)中定義了(le)每→&✔個(gè)刻蝕行(xíng)為(wèi)的(de)允©→±許範圍。因此,可(kě)以根據材料的(de)刻蝕選擇比、橫向比、聚合/錐度∑ 、濺射和(hé)離(lí)子(zǐ)通(tōng)量分(fēn)布等參數(shù)來(lái)™♠₽定義刻蝕行(xíng)為(wèi)。利用(yòng♥λ♦≥)DOE确定的(de)重要(yào)輸入參數(shù),輸入電£≥λ∏(diàn)學性能(néng)指标。 SEMulator3D采用(yòng)直接優化(huà)的(de)方法,以∑&Ω确定WL刻蝕工(gōng)藝中最佳刻蝕步驟行(xín×÷↕g)為(wèi)的(de)工(gōng)藝參數☆©↓&(shù),以滿足電(diàn)學性能(néng)目标。δ↔校(xiào)準工(gōng)藝建議(yì)包₩Ω括氧化(huà)層,矽和(hé)氮化(huà)層的(de)刻蝕選擇比、氧化(huà)≠≠€層和(hé)矽的(de)刻蝕角度和(héσΩ™)選擇比等參數(shù)。 根據這(zhè)些(xiē)結果,可(kě✘α★≤)以通(tōng)過工(gōng)藝研究驗證是(shì)否存在滿足條件(jiàn)的(de)電(•φσ"diàn)學性能(néng),或者在此範圍內(nèi)是(shì)✔'€>否無法實現(xiàn)特定的(de)電(diàn)學性能(néng)。 虛拟工(gōng)藝節省了(le)成本和(hé)時(shí)™β間(jiān) 由于工(gōng)藝假設是(shì)在開(kāi)發♠®×™早期甚至在硬件(jiàn)實現(xiàn)之前完成的(deπ£),因此虛拟工(gōng)藝無需制(zhì)造真正的(de)晶圓,即可(kě₩≈)驗證這(zhè)些(xiē)假設,節省了(le)時(shí)間(jiān)和(hé)費(§∑fèi)用(yòng)。 該DRAM案例研究表明(míng),通(∑>δ÷tōng)過在虛拟環境中執行(xíng)大(dà)量的(de)DOE和(hé)工(gōng)藝變λ♠化(huà)研究,可(kě)以消除不(bù)相(xiàng)關DOE路(lù)徑的(d★♣↑e)時(shí)間(jiān)和(hé)成本,并快(kuài)速實現∏Ω(xiàn)性能(néng)和(hé)良率目标,從(c≥↕óng)而加快(kuài)産品上(shàng)市(sh®∞ì)時(shí)間(jiān)。 |